Historische CPU's / CPUs und LSI aus der Pionierzeit der

Mikroprozessor-Entwicklung:

Motorola (

Thomson EF6802 - 2nd Source) 6802

8bit-CPU mit 128Byte RAM und interner Clock

Links zum nachlesen: Wikipedia: Motorola-CPUs ,Motorola >> 6802

Assembler Beispiele (als Beispiel für frühe Assembler-Programmierung )

finden sich hier:Assembly

Language programming

Sie möchten ein Stück erwerben ( Datenblatt verfügbar ) -> eMail-Kontakt

Signetics / Synertek

2650:

Links zum nachlesen: CPU-World:

Signetics 2650 family , Signetics

2650 - Wikipedia

See "Section

Two: Forgotten/Innovative Designs before the Great Dark Cloud"

....Superficially similar to the PDP8

(and IMS 6100), the Signetics

2650 was based around a set of 8 bit registers with R0 used as an

accumulator, and six other registers arranged in two sets (R1A-R3A and

R1B-R3B) - a status bit determined which register bank was active. The

other registers were generally used for address calculations (ex.

offsets) within the 15 bit address range. This kept the instruction set

simple - all loads/stores to registers went through R0. It also had a

subroutine stack of eight 15 bit elements, with no

provision for spilling over into memory.

Zusammen mit "2636 Programmable Video Interface" als frühe

Videospielkonsole ( Basis-Entwicklung Signetics , vertrieben in

Deutschland als Intercord 2000 XL oder Palladium ) siehe auch Wikipedia

Sie möchten ein Stück erwerben -> eMail-Kontakt

TMS9900 (TMS 9900) Texas

Instruments

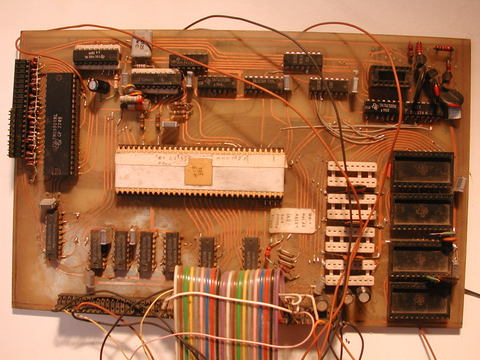

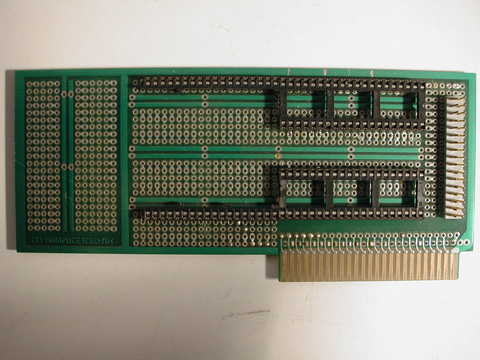

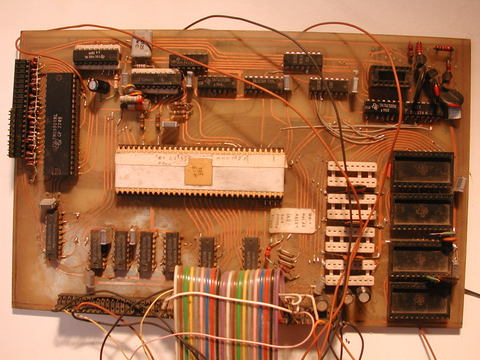

Das PCB ist ein "Homebrew" hergestellte Platine , nachempfunden dem

TM990/100M Entwicklungsboard (PCB) von TI.

funktionstüchtig: (mit 4 * 2114 RAMs und 2 EPROMs mit Monitor-Prog. )

Texas Instruments TMS9900(wikipedia)

..." One of the first true 16 bit microprocessors was the TMS 9900.

It had a 15 bit address space and two internal 16 bit registers.

One unique feature, though, was that all user registers were actually

kept in memory - this included stack pointers and the program counter.

A single workspace register pointed to the 16 register set in RAM, so

when a subroutine was entered or an interrupt was processed, only the

single workspace register had to be changed - unlike some CPUs which

required a dozen or more register saves before acknowledging a context

switch. "

Links: TMS9900

manuals and references

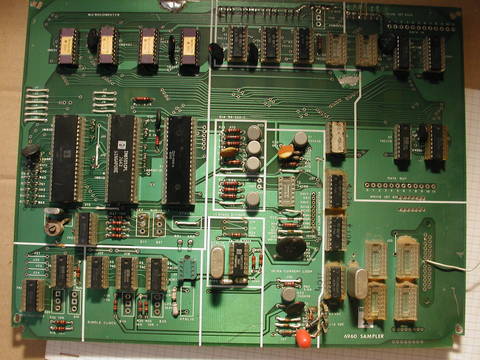

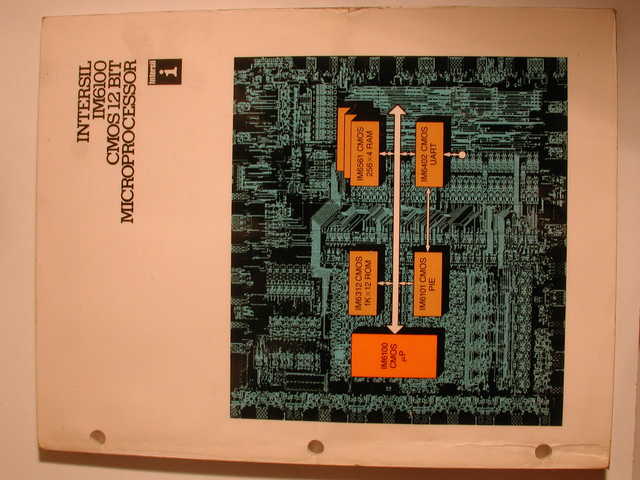

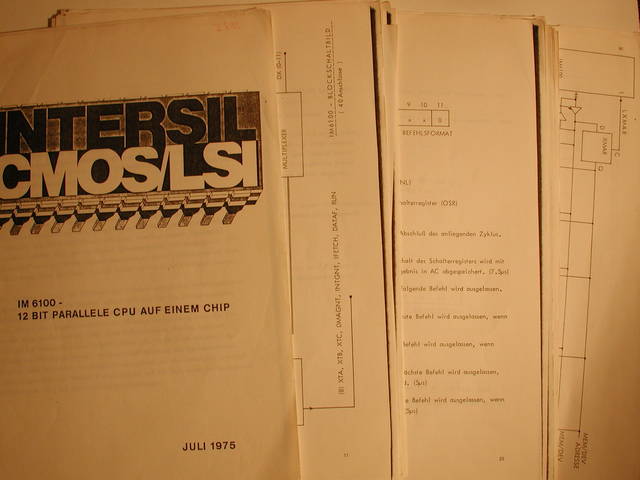

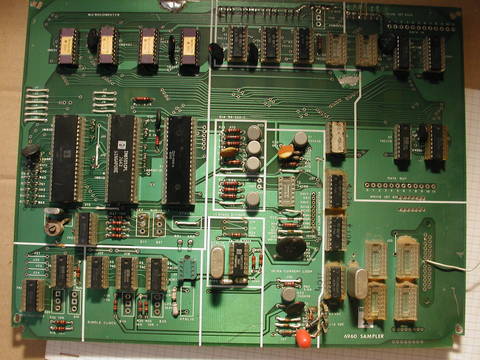

IM6100 Intersil 6960-Sampler

( PDP8-kompatibles Intersil

Sampler-Board! )

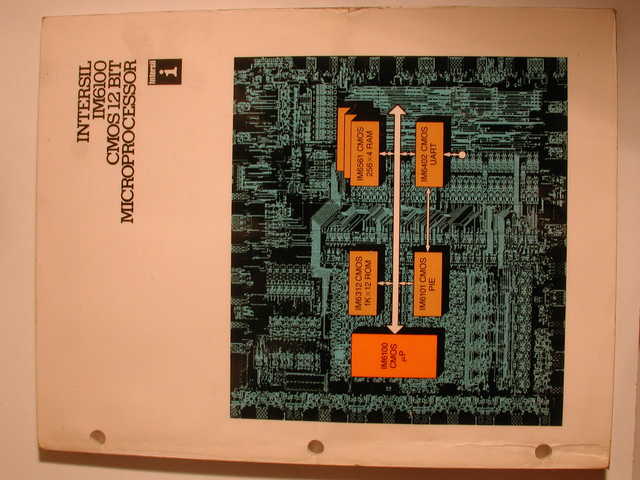

The IM6100 CMOS Family Sampler: PCB w. LSI-Chips IM 6100 C , IM

6403 C

UART , IM 6101 C PIE , IM 6312 C 12K ROM, 3 x IM 6561 C 256 x 4 RAM

inkl. Unterlagen /Datenblätter:

Intersil IM6100 CMOS 12 Bit Prozessor Handbuch - 110 Seiten !

The IM6100 CMOS FAMILY SAMPLER 32 Seiten

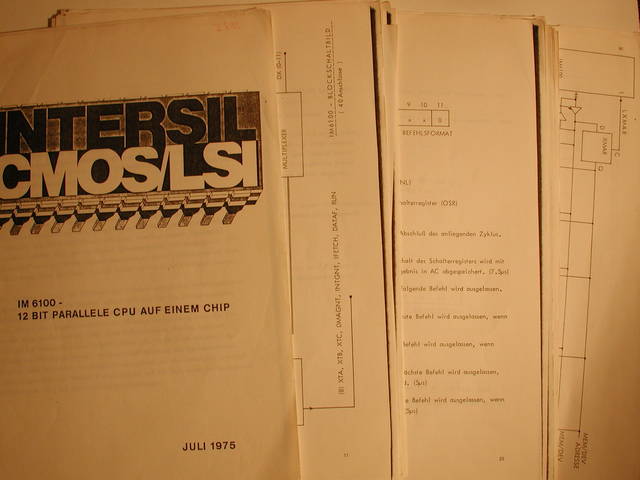

Fotokopie: IM 6100 12BIT Parallele CPU auf einem Chip Juli

1975 , 40 Seiten - deutsch

Fotokopie: IM 6100 Operator Console

Noch weitere Fotokopien: Datenblätter d. Support-Chips,...

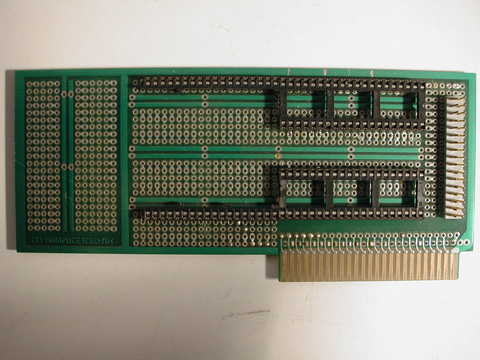

Zum 6960 Mikrocomputer-Board: 6960 Sampler

unbestückt: 2 x 74C00 , 1 x 4069 , ICM 7209 , nachgesetzt:

6 * DIL 16 , 1 * DIL 14 Fassungen ( freier PCB-Bereich mit

großflächigem +5V/GND Kupferflächen wurden genutzt , um weitere Spare

IC-Fassungen für Erweiterungen zu setzen, Für die Pins wurde jeweils

ca. 3mm Durchmesser der Kupferfläche weggebohrt und die 1mm-Bohrung für

die Fassung gesetzt, unverdrahtet )

( you may find more info about pdp8 -command set in alt.sys.pdp8

) Datenblatt IM 6100 CPU: IM6100-Datasheet

Eval-Board fuer die Intersil

IM6100 CPU und diese ist eine PDP8

on Chip. Auf dem Board ist dann auch noch Speicher und ein ROM mit

einem kleinen nano-Debugger sowie eine serielle Schnittstelle mit

legendaeren 110 Baud. Als optionale Erweiterungen kann man noch

IO-Ports bestuecken und es gibt auch eine kleine LED-Console fuer Daten

und Adressen. Mit ein paar Gattern ist auch Single-Clocking und

Single-Instruction auf dem board bestueckbar, so dass er einer

"richtigen" PDP8 schon nahe kommt. Mit CMOS bestueckt und braucht

vollbestückt bei 2MHz lediglich 300mA.

Großes Bild auf Anfrage: -> eMail-Kontakt

6960-SAMPLER

Das 6960-SAMPLER Board ist eine doppelseitig kaschierte Leiterplatte

zur Implementierung eines vollständigen C-MOS Computers unterVerwendung

der im C-MOS FamilySampler Manual beschriebenen Bausteine.

Das Minimalsystem besteht aus der CPU, 256 x 12 RAM,1024 x 12 ROM mit

dem ODT Programm (ASCII Keyboard based Debugging Monitor), einem

seriellen I/O Port und Logic für RUN, HALT und RESET des Systems. Neben

den 7 C-MOS-LSI Schaltkreisen wird eine geringe Anzahl von

Standardschaltkreisen benötigt.

Folgende zusätzliche Funktionen können realisiert werden und sind auf

der Leiterplatte vorgesehen:

~ 20 mA TTY Schnittstelle

~ RS-232-C EIA Schnittstelle

~ 12 bit Eingangsport

~ 12 bit latched Ausgangsport

~ Logik zur Ausführung von Einzelinstruktionen

~ Single Step Clock Logik

~ Monitor für Datenbusinhalt (Adresse, Instruktion, Daten)

~ Monitor für uP Timing Signale

Intersil IM6100 CMOS 12 Bit Prozessor Handbuch - 110 Seiten

!

IM 6100 12BIT Parallele

CPU auf einem Chip Juli

1975 , 40 Seiten - deutsch

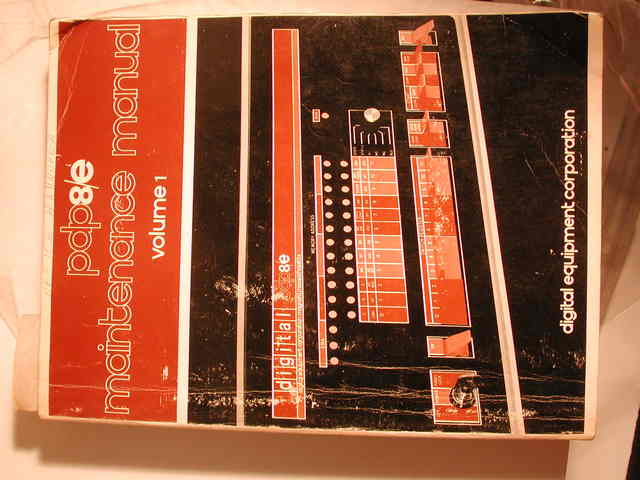

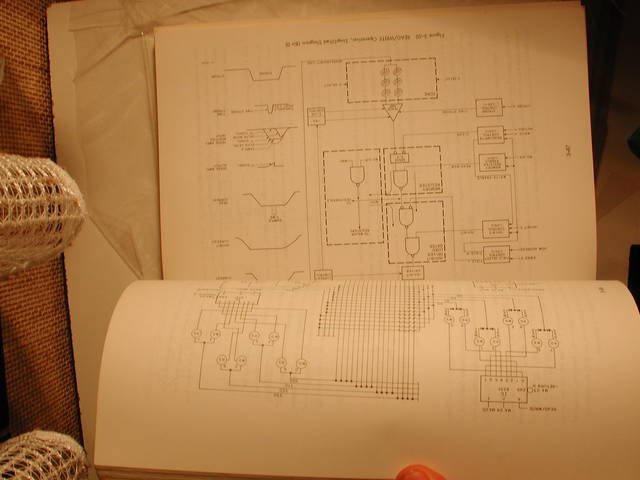

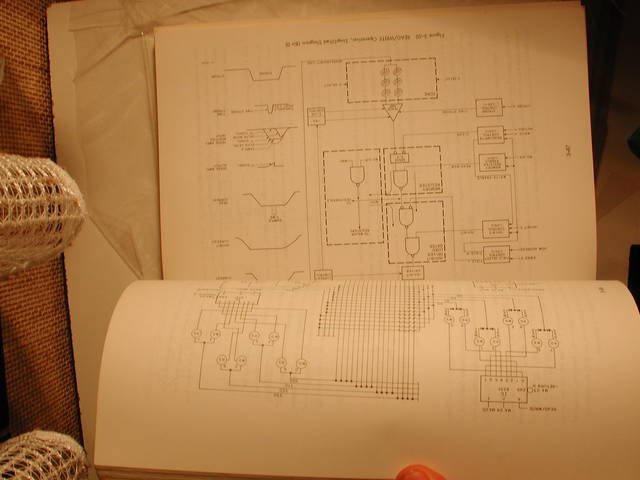

PDP8e

Unterlagen

ct-Magazin-CEPAC (65C02 PCB)

Apple II Protyping / Experimentierplatine: ( 2,54mm

Fassungsreihen bzw. 2* 40pol. Fass. + Pfostenbuchse bereits gelötet !)